如何利用数字化官网来打造数字化市场部

2022-10-13 16:44:36

Features and Applications of Cable Ties

2026-03-18 10:09:28

杭州包车服务

2025-05-31 08:57:46

革新传动电动驱动桥斜齿轮蜗杆卓越

2025-07-02 10:42:41

恒齿传动祝高考生金榜题名

2025-07-04 15:58:33

揭秘拧紧机核心:斜齿轮传动如何重塑装配线

2026-01-09 14:29:30

拼多多出评软件-多多开团助手留评工具

2026-02-28 12:34:43

恒齿 EF 系列:污水处理刮泥机的可靠传动伙伴

2026-04-15 13:18:18

分拣机狂暴节拍 弧齿锥齿低吟 ——机械脉搏里的静默交响

2025-07-29 08:34:14

大功率齿轮减速机:驱动船舶装卸步入高效新纪元

2025-11-03 16:09:12

稀有高科 | 科研制胜之道

2025-07-30 11:37:51

外贸:2026年初首批外贸新规正式落地执行!

2026-01-07 16:16:37

深圳市传帮带企业管理咨询有限公司顺利中标迈瑞医疗代理权

2025-10-28 12:16:18

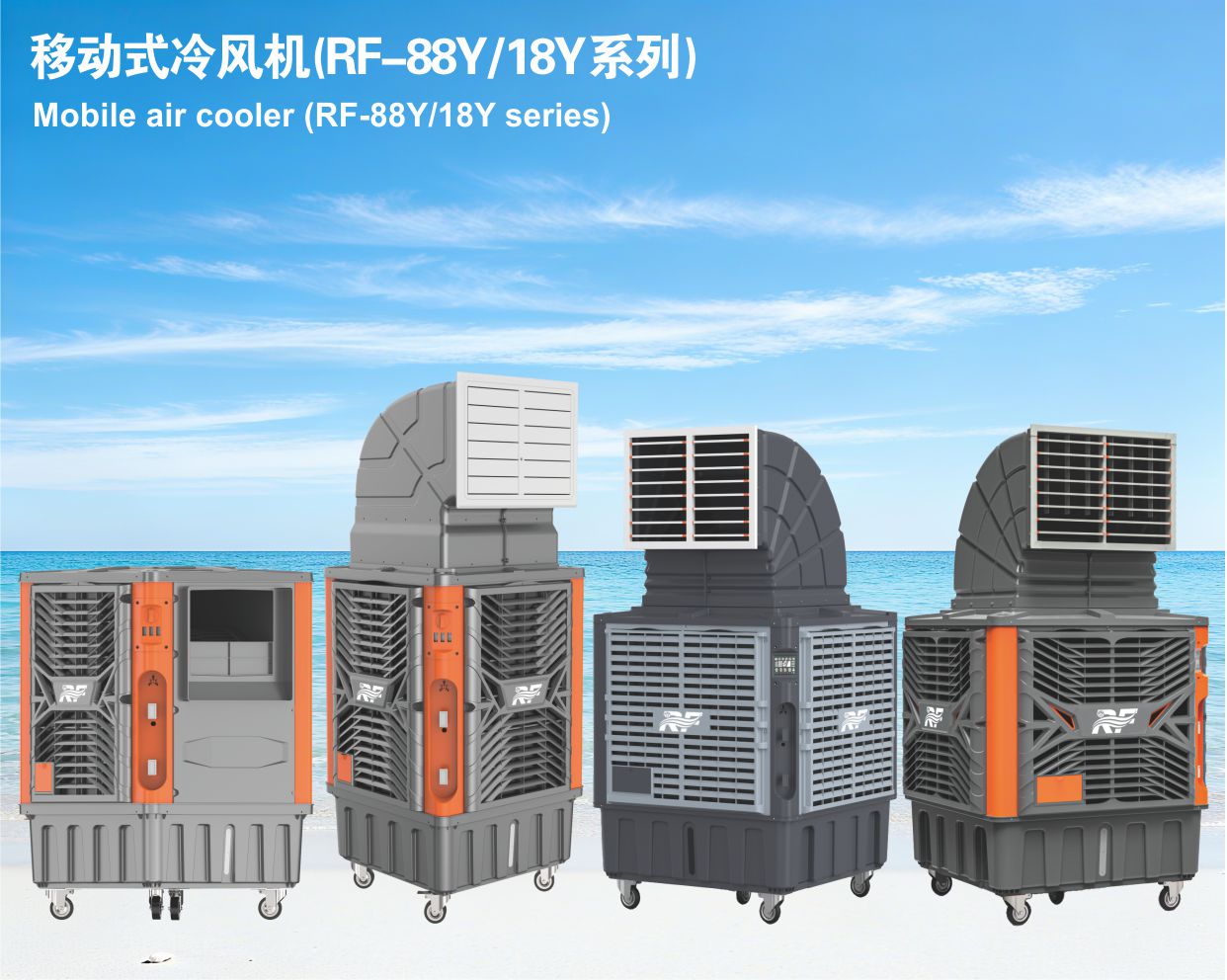

车间降温怎么选?落地扇PK工业大吊扇,瑞峰深度解析

2025-12-11 16:37:05

德鲁克谈领导力,从哪里开始,就从德鲁克对于管理的定义开始!

2026-03-20 10:29:41

甲板起重动力之源 恒齿大功率减速机铸就海工安全屏障

2026-04-16 17:41:03

摊铺机动力跃升之钥:行星齿轮减速机核心技术揭秘

2026-01-15 15:23:53

web3数字化官⽹运营操作指南

2022-09-26 09:52:04

AI流量红利来袭,你的官网准备好了吗?

2026-01-13 18:36:48

华为王者归来!这份大礼包,让美西方原地炸裂!

2023-08-31 07:41:57

夯机强劲动力核心:高功率齿轮减速装置

2025-10-07 10:47:28

#005 子路老师讲官网故事_数字化官网之自适应性

2023-02-15 11:38:53

无人机应用领域的就业岗位全景解析

2025-08-05 09:43:09

齿轮传动 浙超官方合作伙伴 邀您共赴浙超之旅

2025-07-14 16:39:14

营销枢纽云第301次升级 | 可搭建海外商城代购网站 • 一物一码生成规则自定义 • 新增名片管理首页 • 图片/视频素材可快捷搜索

2024-11-25 16:04:51

杭州包车观赏音乐喷泉

2025-05-31 09:00:16

超薄型高摩擦垫片

2026-03-27 14:45:14

DAOLER®:以革新摩擦科技,解锁紧固新境界

2025-12-10 08:12:04

央企国企四类员工,严禁以“不胜任”为由实施末位淘汰

2025-10-27 09:41:53

恒齿减速机维护手册:合成润滑油多久换一次?油封更换全解析(上)

2025-11-13 12:36:15

2026西湖龙井茶官网DTC发售:茶农直供,政府溯源防伪到农户家

2026西湖龙井茶官网DTC发售:茶农直供,政府溯源防伪到农户家